Pedestal/Encoder Interface Board User's Guide

This article describes the antenna encoder interface board developed at CSU-CHILL. This board is designed for use in four different radar systems: CSU-CHILL, CSU-Pawnee, the Solid-state X-band project (WiBEX) as well as the magnetron X-band project. Each of these radars utilize the board to provide an interface between the rotary shaft encoders on each axis of the antenna pedestal, the motion control system and the signal processor.

Introduction

The encoder interface board is designed to be a versatile system, capable of supporting the needs of four rather different radar systems. Each radar system is a particular use-case, and these are listed below.

Use Cases

- CSU-CHILL

- Here, two 15-bit SICK-Stegman ARS-20 SSI encoders are available (one per axis). These must interface to the Delta Tau Turbo PMAC parallel interface board, providing parallel angles that the Delta Tau system uses for position feedback. The Delta Tau system is enclosed within a 3U Eurocard chassis with a 96-pin Eurocard connector, which is used to obtain DC power for the encoder interface board. This also restricts the form factor of the board. A digital output in the form of a self-clocked serial stream using differential TTL signalling is required to provide the signal processor with antenna position information.

- CSU-Pawnee

- The use-case for this radar is not fully defined, since the motion-control system is currently undergoing an update. The motion controller currently in use is a MicroVAX II with a custom interface board that drives the servo amplifiers, and receives 16-bit parallel TTL angles. We are upgrading this system to use a Turbo PMAC, as with CHILL. The current position feedback system in use has 60 Hz AC synchros, and uses a synchro-to-digital converter module. Again, the form-factor is restricted to 3U Eurocard.

- WiBEX

- WiBEX is the internal name of the solid-state X-band project. This radar uses an SCR-584 pedestal, brushless DC motors from Parker-Hannifin, and ARS-25 SSI encoders from SICK-Stegmann. The motors are driven using two Advanced Motion Controls digital servo drives. The board must be able to drive the 24VDC brake solenoids on the brushless motors. The signal processor interface is similar to CHILL, using a self-clocked differential TTL signal. In addition, system monitoring capability is required, through a Modbus/RTU interface. Finally, a method to manually control the antenna position, using an external serial device, must be provided.

- Barcelona Magnetron X-band system

- The antenna controller of the Barcelona radar has the same requirements as WiBEX, except for the system monitoring capability, and the signal processor interface. Instead of using a self-clocked serial stream, this radar uses an RS485 interface to provide antenna position updates to the signal processor.

Block Diagram

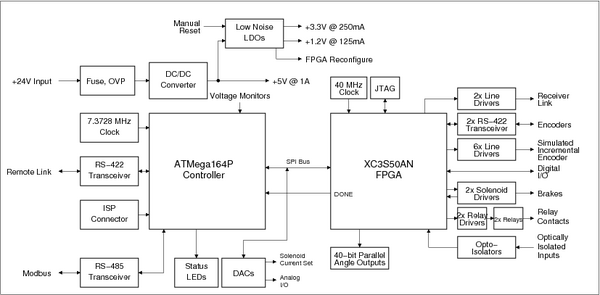

The figure below shows a block diagram of the interface board.

Block Diagram

A Xilinx XC3S50A FPGA provides the majority of the interface functions. The FPGA interfaces to two encoders using the SSI protocol. Appropriate line drivers and receivers are provided to interface with the encoders. The number of bits supported by the encoders is determined by the FPGA firmware. Two Simulated Incremental Encoder Interfaces are provided, these permit the FPGA to provide the digital servo drives with position feedback. The FPGA drives two 16-bit parallel interfaces, suitable for driving parallel angles to an external device. Two relays are provided, for high current/high voltage applications. Two DRV104 solenoid drivers permit the FPGA to drive 24V brake solenoids present on drive motors. Four opto-isolators are provided, for isolated digital input capability (such as for limit switches, manual stops, etc). The FPGA has an independent 40 MHz clock.

An Atmel ATMega164P behaves as the system controller for the board. The MCU interfaces to the FPGA using the SPI bus. Registers internal to the FPGA may thus be modified. The MCU offers two serial ports, one is used to provide an RS485 interface. In the WiBEX use-case, this interface allows Modbus/RTU monitoring to occur, while in the Barcelona radar, this port is used for antenna angles. The second serial port is used for the remote interface, through which the pedestal can receive manual commands. The MCU SPI bus is also used to control an AD8801 8-channel DAC. The MCU is clocked at 7.3728 MHz.

Components

Power Supply

The primary power supply in the CSU-CHILL configuration comes from the bus voltages present on the UMAC chassis. The +15V supply is used to drive the SSI encoders, while the +5V supply is used for the digital logic. In the other two configurations, an external +24V power supply is required, which is used for the motor brake drive and SSI encoders. The 24V supply is then stepped down using a DC/DC converter, to +5V. A TPS70745 low-dropout (LDO) linear regulator provides +3.3V and +1.8V from this supply, for the FPGA I/O and core voltages. The dual LDO provides power sequencing, and also generates power-on reset signals for both the FPGA and the microcontroller. Two manual reset signals are provided, one of which is brought to a connector while the other connects to a board-mounted reset switch. Either manual reset forces the FPGA to reconfigure itself.

FPGA

The FPGA selected is the Xilinx 3S50A, in a 144-pin TQFP package. This FPGA provides a large number of gates at low cost, and has built-in Flash for bitstream storage, thus the FPGA does not require external Flash or PROMs.

The FPGA interfaces with the SSI encoders, simulated encoder outputs, GPIOs, drive links, solenoid drivers, relays and GPIOs through a variety of interface logic, described below. The logic of performing data translations is handled by the FPGA, while control functions are carried out by the MCU.

The FPGA converts the input absolute encoder data into an offset absolute value, based on the azimuth and elevation offset registers. These are then converted to an incremental form, suitable for the AMC drives on the WiBEX and Magnetron radars. The FPGA also does the conversion to 16-bit parallel form, suitable for the CSU-CHILL and CSU-Pawnee configurations. Finally, the FPGA also performs a conversion to the self-clocked stream suitable for the CHILL, Pawnee and WiBEX signal processors.

The FPGA permits the board's available digital I/O resources (optocouplers, relays, solenoid drivers and digital I/O ports) to be shared among the two servo drives. Any logical combination can be performed, as needed, by the FPGA.

A 40 MHz clock is connected to an FPGA global clock input (GCLK8), which may be used to drive an onboard Digital Clock Manager (DCM) on the FPGA. Note that any crystal of frequency > 24 MHz (DC minimum frequency) may be used in place of U6, with a 5 x 3.2 mm footprint. Abracon ASFL1 series is suggested.

Microcontroller

The board uses an Atmel ATMega164P microcontroller unit (MCU) to perform system monitoring and interface functions. The MCU was chosen since it has sufficient Flash memory for program storage and sufficient SRAM to execute a Modbus/RTU stack.

A second UART allows simultaneous use of both Modbus/RTU as well as a remote communications interface. The remote interface is provided to allow attachment of an external hand-held controller to permit manual control over the antenna. The hand-held controller link is through differential-mode (RS-422) signalling, to improve noise immunity. The board provides +5V DC to the remote controller, through a ferrite bead (for conducted noise isolation) and a 160 mA fuse, to prevent damage in the event of a cable or controller failure.

Three LEDs are connected to the controller GPIOs. For each LED position, a board-mounted LED is available, along with a current-limited connection (J33) to permit connecting an external LED (for example, a panel-mount type).

The MCU's internal ADC is used to measure three supply voltages (input supply (after filtering), +5V and +3.3V rails). In order to permit noise-free measurements, the ADC supply voltage is filtered through an LC network (L1, C1).

The MCU is programmed through an ISP connector (J2), and uses a 7.3728 MHz crystal oscillator (to permit accurate setting of serial port baud rates).

SSI Encoder Interface

The encoders used to sense the antenna position are compatible with the Synchronous Serial Interface (SSI) standard developed by SICK-Stegmann. Their ARS-20 and ARS-25 absolute encoders provide an SSI formatted output. The interface board must drive a clock signal, and receives the SSI data in response. The interface uses differential TTL signalling. In order to protect the interface from ESD events or accidental high voltages, a protection network is used, consisting of a 22 ohm series resistor and 6.8V transorbs. The resistors act as a ballast (and possibly a fuse), while the transorbs protect the differential receivers from damage. A common mode choke is used, to improve common mode interference rejection of the differential signals.

In addition to the clock and data lines, two single-ended signals are provided for clockwise/counterclockwise selection, as well as a zeroing input. These, too, are protected using series ballast and transorbs. A ferrite bead is used to filter out high frequency interference.

Finally, +24V DC power is provided to each encoder through a ferrite bead and a 160 mA resettable fuse. The ferrite bead isolates conducted high-frequency noise, while the fuse protects the interface board in the event of a cable or slip-ring failure.

Drive Interface

Four connectors (J9-J12) are used to interface to the servo drives. Each drive has two digital I/O connectors, which correspond to each pair (J9-10, J11-12) of connectors on the interface board. Each drive has a simulated incremental encoder port, used for position feedback, and a general-purpose I/O port.

Simulated Incremental Encoder Interface

The simulated incremental encoder interface is provided to interface to the AMC drives used on the WiBEX and Magnetron radar projects. These drives require an incremental encoder input, which is generated by the FPGA from the SSI encoder inputs. The simulated encoder outputs are driven by 26LV31 differential TTL driver chips. These provide high drive strength and fault tolerance. In order to improve fault tolerance, external 22 ohm series resistors and transorbs are provided. Ferrite beads are used on each line to improve noise immunity. The outputs are driven using a 26LV31 (U15,16) driver, which is in turn driven by the FPGA.

General Purpose I/O

The GPIO port for each drive has seven digital inputs and four digital outputs. The drive provides four analog input connections, one of which is on the motor feedback connector (usually used to sense motor temperature). Of the remainder, inputs 1 and 4 are available to the board. Input 4 is driven by onboard DACs, while input 1 of each drive is connected to the common I/O port. Similarly, the analog output provided by each drive is connected to the common I/O port.

The digital I/O lines are connected to the FPGA. The FPGA can thus perform various logic operations on these lines, and use the results to drive various I/O peripherals, as described in the following sections. Each I/O is protected using a 22 ohm series resistor.

DAC

The interface board provides an eight-channel DAC under control of the Atmel MCU. Two channels are used to set the holding current of the DRV104 solenoid drivers. Four channels drive the analog inputs of each of the AMC drives. Each input requires two channels, in order to have a differential analog drive capability. The DAC has an internal reference voltage generator, and has its own power supply LC filter (L2, FB14, C36-38).

Digital I/O Interfaces

The board provides various different digital I/O peripherals. These are shared between the two drives, so they are routed through the FPGA.

Solenoid Driver

Two DRV104 solenoid drivers are provided, these permit the onboard FPGA to drive two external solenoids with up to 24VDC at 1.2A. The intended load is a solenoid, since the driver provides a high initial pull-in current, and then limits the holding current using a PWM waveform. The MCU can adjust this holding current using the DAC. The solenoid driver provides a feedback signal that indicates, to the FPGA, that the coil current < 2A, and the DRV104 driver temperature does not exceed safe values. A 2A flyback diode is provided on each output, to short circuit kickback from inductive loads.

Opto-isolator

Four opto isolators are provided, which allow external signals to be safely monitored. Each input is tied to an input on the common I/O port through a series resistor. By adjusting the resistor (as shown on the schematic), the input voltage range may be altered.

Relays

Two electromechanical SPDT relays are provided on the board. Each relay has an associated MOSFET driver circuit, which is driven by the FPGA. The relay contacts are rated for 2A@30V, or 0.2A@110V. All three contact terminals are brought out to the common I/O connector.

FPGA Firmware

This section describes the logic implemented on the board's FPGA.

Block Diagram

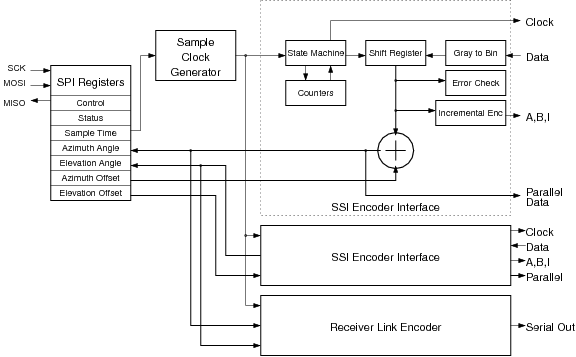

A block diagram of the FPGA logic is presented below.

FPGA Logic Block Diagram

The FPGA implements four major blocks. An SPI block implements several registers that can be read or written through an SPI bus. The registers, when read, reflect the state of the board. Writing the registers can affect the board operation. A sample clock generator produces a regular sampling frequency that is used to poll the absolute encoders. Finally a pair of encoder interface blocks read each absolute SSI encoder, produce a binary parallel version of the encoder output and convert the output to an incremental version suitable for the WiBEX drives. In addition, the digital input/output lines from the drives are routed to various I/O devices on the board, as well as to SPI registers.

SPI Block

The SPI block implements various read/write registers that may be read or written by the microcontroller through the SPI bus.

| R/W | Address | Register | Description | Power-on default |

|---|---|---|---|---|

| Read/Write | 0x00 | CONTROL | Control digital I/O, clear errors, etc | 0x00 |

| Read | 0x01 | STATUS | Read errors, drive digital output status, optocoupler status | N/A |

| Write | 0x01 | SAMPLE_TIME | Sample timer maximum count | 1450 |

| Read | 0x02 | AZ_ANGLE | Absolute azimuth angle | N/A |

| Write | 0x02 | AZ_OFFSET | Azimuth angle encoder zero offset | 0 |

| Read | 0x03 | EL_ANGLE | Absolute elevation angle | N/A |

| Write | 0x02 | EL_OFFSET | Elevation angle encoder zero offset | 0 |

Register list

Control Register

| Bits | Name | Description | Power-on default |

|---|---|---|---|

| 15 | Manual Relay 2 | Manual Control over relay 2, if the relay control source bit is set to 1 | 0 |

| 14 | Manual Relay 1 | Manual Control over relay 1, if the relay control source bit is set to 1 | 0 |

| 13 | Elevation CW/CCW | Controls if the encoder count increments when the shaft turns clockwise (0) or counterclockwise (1) | 0 |

| 12 | Reserved | 0 | |

| 11 | Elevation CW/CCW | Controls if the encoder count increments when the shaft turns clockwise (0) or counterclockwise (1) | 0 |

| 10 | Reserved | 0 | |

| 9 | Autoclear errors | Clear error bits when encoders cross the zero mark | |

| 8 | Clear errors | Set to 1 to clear errors. Bit must be manually cleared after being set. | 0 |

| 7-5 | Digital Inputs 7-5 | Controls the state of digital inputs 7-5 on both azimuth and elevation drives | 0 |

| 4 | Brake control source | Set to 1 allow the FPGA to control the brake driver, set to 0 to allow brake control to be assigned to digital output 1 of each drive. | 0 |

| 3 | Manual Brake control | If the brake source is set to 1, this bit enables the brake solenoid driver when set to 1, disables it when set to 0. | 0 |

| 2 | Relay control source | Set to 1 allow the FPGA to control the relays, set to 0 to allow relay 1 to be driven by digital output 2 of the azimuth drive, and relay 2 to be driven by digital output 2 of the elevation drive. | 0 |

| 1,0 | Reserved | 0 | |

Control Register

Status Register

| Bits | Name | Description |

|---|---|---|

| 15 | Optocoupler 2 | State of Optocoupler input 2 |

| 14 | Optocoupler 1 | State of Optocoupler input 1 |

| 13-10 | Elevation digital outputs 4-1 | State of digital outputs from the elevation drive |

| 9-6 | Azimuth digital outputs 4-1 | State of digital outputs from the azimuth drive |

| 5 | Elevation conversion error | Shaft moving too fast for incremental encoder conversion. |

| 4 | Elevation encoder LED error | Set when elevation encoder LED fails or it reports a positioning failure |

| 3 | Elevation brake driver error | Set if the elevation brake driver reports an overcurrent or overtemperature condition. |

| 2 | Azimuth conversion error | Shaft moving too fast for incremental encoder conversion. |

| 1 | Azimuth encoder error | Set when azimuth encoder LED fails or it reports a positioning failure |

| 0 | Azimuth brake driver error | Set if the azimuth brake driver reports an overcurrent or overtemperature condition. |

Status Register

Note that the error bits are persistent, and will not be cleared unless either auto-clear mode is enabled, or a clear command is issued by writing the clear errors bit in the control register.

Angle Registers

These registers allow the host MCU to read the 16-bit offset corrected angles from the two encoders.

Offset Registers

These registers allow the host MCU to set the 16-bit encoder zero offsets.

Sample Clock Generator

The sample clock generator produces a periodic encoder sample signal. The time period of this signal may be adjusted by writing to the SAMPLE_TIME register on the FPGA. The value represents the time interval between successive sampling instants, in units of 25 ns. The power-on default value of 1450 results in a sampling interval of 36.25 us, or a sampling rate of 27.5 kHz. The minimum sample period is defined by the time taken to send out 17 clocks (17 us, for a 1 MHz encoder clock) and the 20 us delay time required between successive samples of the encoder.

Encoder Interface Blocks

The encoder interface blocks incorporate a majority of the FPGA functionality. One encoder interface block is provided for each axis.

An SSI encoder interface sub-block generates a clock signal (nominally 1 MHz) to read the encoder. The received serial data stream from the encoder is converted from a gray coded version to a 15-bit binary word. Two additional bits read back from the encoder are error bits used to detect conversion or light-source errors reported by the encoder. The errors are latched by a resettable flip-flop, so that transient errors may be detected.

The raw angles are sent to an incremental encoder driver. This module generates a simulated incremental encoder output from the raw 15-bit input. The operation of this block depends on the 15-bit absolute angle inputs increasing or decreasing without missing codes. Missing codes are the result of the encoder shaft moving so fast that the sample clock generated by the sample clock generator is not sufficient to detect every code change. The incremental encoder driver will detect such conditions and set an error flag, which is again latched by a resettable flip-flop to catch transient errors.

If the autoclear errors bit is clear in the status register, the conversion error reported by the incremental encoder driver is cleared only if the clear errors bit in the status register is set. Otherwise, the block waits for the angle to reach zero before the error is cleared.

The 15-bit parallel angles are converted to 16-bit by left-shifting. A 16-bit zero-offset is added to the raw angle to produce a corrected angle, which is available at the parallel output of each converter.

Connectors

This section lists the connectors available on the board.

Common I/O connector

The common I/O connector is a set of I/Os common to both the azimuth and elevation drives. These may be interfaced to, for example, limit switches and other sensors. These signals are routed to the digital inputs and outputs of the two drives via the FPGA.

These signals are made available on two 14-pin connectors on the board, which in turn are connected to a 28-pin CPC chassis-mount connector. The table below shows the pinouts for both. Finally, a cable connects the chassis-mount connector to a terminal block. The terminal block numbers are also indicated below.

| CPC | Board | Purpose | Terminal Block | |

|---|---|---|---|---|

| Pin | Conn | |||

| 1 | 5 | J8 | Elevation Analog Input+ | TB-6-1 |

| 2 | 12 | J7 | Azimuth drive, analog output- | TB-4-6 |

| 3 | 3 | J8 | Azimuth Analog Input+ | TB-4-1 |

| 4 | 1 | J8 | +24V DC Input | TB-1-3 |

| 5 | 6 | J8 | Elevation Analog Input- | TB-6-2 |

| 6 | 14 | J7 | Elevation drive, analog output- | TB-6-6 |

| 7 | 4 | J8 | Azimuth Analog Input- | TB-4-2 |

| 8 | 2 | J8 | +24V DC Input Return | TB-1-6 |

| 9 | 14 | J8 | Opto4+ | TB-5-7 |

| 10 | 12 | J8 | Opto3+ | TB-5-5 |

| 11 | 10 | J8 | Opto2+ | TB-5-3 |

| 12 | 8 | J8 | Opto1+ | TB-5-1 |

| 14 | 1 | J7 | Elevation Brake+ | TB-6-3 |

| 13 | 3 | J7 | Azimuth Brake+ | TB-4-3 |

| 15 | 13 | J8 | Opto4- | TB-5-8 |

| 16 | 11 | J8 | Opto3- | TB-5-6 |

| 17 | 9 | J8 | Opto2- | TB-5-4 |

| 18 | 7 | J8 | Opto1- | TB-5-2 |

| 20 | 2 | J7 | Elevation Brake- | TB-6-4 |

| 19 | 4 | J7 | Azimuth Brake- | TB-4-4 |

| 21 | 8 | J7 | Relay 2, Normally Closed | TB-6-12 |

| 22 | 10 | J7 | Relay 2, Common | TB-6-11 |

| 23 | 11 | J7 | Azimuth drive, analog output+ | TB-4-5 |

| 24 | 6 | J7 | Relay 1, Common | TB-4-11 |

| 25 | 7 | J7 | Relay 1, Normally Closed | TB-4-12 |

| 26 | 9 | J7 | Relay 2, Normally Open | TB-6-10 |

| 27 | 13 | J7 | Elevation drive, analog output+ | TB-6-5 |

| 28 | 5 | J7 | Relay 1, Normally Open | TB-4-10 |

Common I/O Connector

Drive Link

The drive links connect the interface board to the digital I/O connector and auxiliary encoder connector on the drives.

These signals are made available on two 14-pin connectors on the board, which in turn are connected to a 28-pin CPC chassis-mount connector. This connection is made through a CPC connector sub-assembly. There are two connector pairs, one for each axis. A cable connects this CPC chassis-mount connector to the digital I/O and auxiliary encoder connectors on the drives. The table below shows the pinouts for all connectors involved.

| CPC | Board | Purpose | Drive | ||

|---|---|---|---|---|---|

| Pin | Conn | Pin | Conn | ||

| 1 | J9/J11 | 1 | Feedback A+ | Aux Enc | 4 |

| 2 | J9/J11 | 3 | Feedback B+ | Aux Enc | 6 |

| 3 | J9/J11 | 5 | Feedback Index+ | Aux Enc | 8 |

| 4 | J9/J11 | 7 | Feedback Ground | Aux Enc | 10 |

| 5 | J9/J11 | 2 | Feedback A- | Aux Enc | 5 |

| 6 | J9/J11 | 4 | Feedback B- | Aux Enc | 7 |

| 7 | J9/J11 | 6 | Feedback Index- | Aux Enc | 9 |

| 8 | J9/J11 | 8 | Feedback Ground | Aux Enc | 11 |

| 9 | J9/J11 | 9 | Analog Input 4+ | Aux Enc | 14 |

| 10 | J9/J11 | 10 | Analog Input 4- | Aux Enc | 15 |

| 11 | J9/J11 | 11 | Analog Input 1+ | Digital I/O | 4 |

| 12 | J9/J11 | 12 | Analog Input 1- | Digital I/O | 5 |

| 13 | J9/J11 | 13 | Analog Output | Digital I/O | 7 |

| 14 | J9/J11 | 14 | Analog Ground | Digital I/O | 16 |

| 15 | J10/J12 | 4 | Digital Output 4 | Digital I/O | 14 |

| 16 | J10/J12 | 3 | Digital Output 3 | Digital I/O | 10 |

| 17 | J10/J12 | 2 | Digital Output 2 | Digital I/O | 3 |

| 18 | J10/J12 | 1 | Digital Output 1 | Digital I/O | 1 |

| 19 | J10/J12 | 5 | Digital Ground | Digital I/O | 26 |

| 20 | J10/J12 | 6 | Digital Output Common | Digital I/O | 2 |

| 21 | J10/J12 | 7 | Digital Input 1 | Digital I/O | 11 |

| 22 | J10/J12 | 8 | Digital Input 2 | Digital I/O | 12 |

| 23 | J10/J12 | 9 | Digital Input 3 | Digital I/O | 13 |

| 24 | J10/J12 | 10 | Digital Input 4 | Digital I/O | 17 |

| 25 | J10/J12 | 11 | Digital Input 5 | Digital I/O | 9 |

| 26 | J10/J12 | 12 | Digital Input 6 | Digital I/O | 18 |

| 27 | J10/J12 | 13 | Digital Input 7 | Digital I/O | 19 |

| 28 | J10/J12 | 14 | Digital Input Common | Digital I/O | 15 |

Drive Link Connector

The cable harness for the drive link shall have two branches, one with the Digital I/O connections, the other with the Auxiliary Encoder connections. Signals with the +/- designation use a twisted-pair to reduce noise pickup.

Encoder

The encoder connections permit two SSI-compatible absolute encoders to be attached to the board.

These signals are made available on a 10-pin connector, which is then interfaced to an 8-pin chassis-mount CPC connector via a CPC connector subassembly. A cable connects this CPC connector to a 12-pin M23 connector on the encoder body. The table below shows the pin numbers for the board-mount 10-pin connectors (J5/J6), the CPC connector and the M23 connector.

| CPC | J5/J6 | M23 | Purpose |

|---|---|---|---|

| 1 | 1 | 8 | Power Supply |

| 2 | 2 | 1 | Ground |

| 3 | 3 | 2 | Data+ |

| 4 | 9 | 9 | Set Zero |

| 5 | 7 | 3 | Clock+ |

| 6 | 4 | 10 | Data- |

| 7 | 10 | 5 | CW/CCW |

| 8 | 8 | 11 | Clock- |

| N/C | N/C | Case | Shield |

Encoder Connector

Signals with the +/- designation use a twisted-pair to reduce noise pickup. The cable shield shall be connected to the conector case of the M23 connector at the encoder end.

Receiver Link

The receiver link connection is a two-bit differential TTL high-speed serial link to the receiver/signal processor. This may be used for reading the antenna position for data tagging. The connector also contains Modbus/RTU control bus signals.

These signals are made available on a 10-pin connector, which is then interfaced to a male 9-pin chassis-mount CPC connector via a CPC connector subassembly. The table below shows the pin numbers for the board-mount 10-pin connector (J15), the CPC connector and serial connector signals.

| The adapter board between the ribbon cable and the CPC connector has an error, the table below shows the corrected CPC pins. |

| CPC | J15 | Purpose |

|---|---|---|

| 1 | 2 | Rx Link 1- |

| 2 | 8 | Rx Link 2- |

| 3 | 4 | Rx Link 1+ |

| 4 | N/C | Unused |

| 5 | 5/6 | Modbus/RTU Ground |

| 6 | 9 | NC (Rx Link 2+, after bridging to pin 10 on J15) |

| 7 | 3 | Modbus/RTU A |

| 8 | 7 | Modbus/RTU Alarm |

| 9 | 1 | Modbus/RTU B |

Receiver Link

Signals with the +/- designation and the Modbus/RTU A/B use a twisted-pair to reduce noise pickup.

Servo Amp Resolver Feedback

The Feedback signals on the Servo Amp are made available on a 15-pin HD-22 connector, which is then interfaced to a male 17-pin M23 connector via a M23 connector subassembly. The table below shows the pin numbers for the 15-pin connector (FDBK), the M23 connector and feedback signals.

| FDBK | Wire Color | M23 | Purpose |

|---|---|---|---|

| 4 | RED/BLU | 14 | REF OUT + |

| 5 | GRY/PNK | 17 | REF OUT - |

| 6 | YLW/BRN | 2 | SIN + |

| 7 | WHT/YLW | 1 | SIN - |

| 8 | BRN | 11 | COS + |

| 9 | WHT | 12 | COS - |

| 13 | PNK | 13 | +5V OUT |

| 14 | GRY | 9 | PAI-3 |

Servo Amp Feedback Connector

Modbus

The interface to the board is through Modbus/RTU. The Modbus communications model is a single master controlling various slave devices[1]. Each slave is addressable, and has different registers which may be read or written. This design implements read-only registers (referred to as Input Registers in the Modbus specifications) and read-write registers (Holding Registers). There are no coils or status bits available.

The default Modbus address is set to 0x40. This may be changed by re-compiling the microcontroller code, if desired.

Input Registers

The available input registers are shown in the table below:

| Register Number | Name | Description |

|---|---|---|

| 1000 | ALARM | Indicates the cause of any alarms indicated by the Modbus ALM signal. Reading the register clears the alarm condition and deasserts the Modbus ALM signal. |

| 1001 | STATUS | Indicates the current status of the board. |

| 1002 | AZ_ANGLE | Read back the current azimuth angle from the encoders. This includes any offsets added by the FPGA. |

| 1003 | EL_ANGLE | Read back the current elevation angle from the encoders. This includes any offsets added by the FPGA. |

| 1004 | V_INPUT | Input voltage to the board, should be nominally 24V. The voltage is read back in millivolts. |

| 1005 | V_REG | Voltage after the switch mode regulator, should be nominally 5V. The voltage is read back in millivolts. |

| 1006 | V_CPU | Voltage supply to the microcontroller, should be nominally 3.3V. The voltage is read back in millivolts. |

Input Register Map

Alarm Register

This register contains bit values that may be used to determine the cause of an alarm/fault. The bits are described below.

| Bit | Name | Description |

|---|---|---|

| 1 | Voltage fault | The measured voltages have fallen out of tolerance |

| 0 | Encoder fault | The encoders have reported either a position or LED fault. |

ALARM register (address 1000)

Holding Registers

The available holding registers are shown in the table below:

| Register Number | Name | Description |

|---|---|---|

| 1000 | FPGA Control Register | Read/write the FPGA Control register, described in the section above. |

| 1001 | Encoder Sample Time | Read/write the Encoder sampling interval register in the FPGA, as described in the FPGA registers section. |

| 1002 | Azimuth Offset | Read/write the Azimuth encoder offset. |

| 1003 | Elevation Offset | Read/write the Elevation encoder offset. |

| 1004 | Azimuth Analog Channel | Read/write the value of the azimuth analog channel. This gets written to the DACs and is connected to the Analog Input 4 of the azimuth drive. The value ranges from -255 to +255. |

| 1005 | Elevation Analog Channel | Read/write the value of the elevation analog channel. This gets written to the DACs and is connected to the Analog Input 4 of the elevation drive. The value ranges from -255 to +255. |

| 1006 | Brake Duty Cycle | Read/write brake duty cycle. This register controls the ON-time duty cycle of the brake driver. The value ranges between 0-255, with 0 having the least duty cycle and 255 the most. |

Holding Register Map

Jumpers

This section describes the jumpers available on the board to modify the board behavior.

FPGA configuration mode selection

| Pins | Mode | ||

|---|---|---|---|

| 5-6 (M2) | 3-4 (M1) | 1-2 (M0) | |

| x | Internal Master SPI | ||

| x | JTAG | ||

FPGA Configuration Mode

The normal operation mode is Internal Master SPI, where the FPGA will configure itself from its internal SPI Flash. The JTAG mode allows for quick FPGA development, but the stored configuration will be lost on power-cycling the board. Note that the DONE LED will switch on only after the FPGA has correctly configured itself from a configuration source.

The configuration modes indicated are the only ones supported by the board. Other combinations of configuration mode jumpers will result in an inoperative board and possible damage.

Other Resources

References

- ↑ http://www.modbus.org/specs.php Modbus specifications